# P400 SYSTEM REFERENCE User Guide

Revision PRELIM. A 13 JULY 1976

145 Pennsylvania Ave. Framingham, Mass. 01701 Copyright 1976 by Prime Computer, Incorporated 145 Pennsylvania Avenue Framingham, Massachusetts Ø1701  $(h_{i}^{*})^{(i)} \in [h_{i}^{*}] \in [h_{i}^{*}]$

Performance characteristics are subject to change without notice.

2

# CONTENTS

| Secti                                                                                               | ion Title                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page       |                                                                                                            |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------|

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>———</b> |                                                                                                            |

| 1. I                                                                                                | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                               | ••••       | 1-1                                                                                                        |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8                                                | Introduction to This Document.<br>Introduction to the PRIME 400 Processor.<br>Compatibility.<br>Performance.<br>Input/Output Operation.<br>Firmware Enhancements.<br>Integrity Enhancements.<br>Implementation.                                                                                                                                                                                                                                            |            | $1-1 \\ 1-1 \\ 1-2 \\ 1-6 \\ 1-7 \\ 1-8 \\ 1-10 $                                                          |

| 2. P                                                                                                | PROGRAM-VISIBLE DECOR.                                                                                                                                                                                                                                                                                                                                                                                                                                     | • • • • •  | 2-1                                                                                                        |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12<br>2.13<br>2.14 | <pre>Virtual Memory Structure.<br/>PRIME 400 Instruction Set.<br/>PRIME 400 Effective Address Calculation<br/>Generic-AP Instructions.<br/>Field Manipulation Instructions.<br/>Procedure Call<br/>Double-Precision Integer Changes.<br/>Double-Precision Floating-Point Changes.<br/>Condition Codes and L-Bit<br/>Keys and Modals.<br/>Process Exchange.<br/>Traps, Interrupts, Faults, and Checks<br/>Queues and DMQ.<br/>Other New Instructions.</pre> | •••••      | 2-1<br>2-3<br>2-16<br>2-29<br>2-29<br>2-42<br>2-42<br>2-42<br>2-43<br>2-44<br>2-47<br>2-55<br>2-65<br>2-70 |

| 3.                                                                                                  | CONTROL PANEL                                                                                                                                                                                                                                                                                                                                                                                                                                              | • • • • •  | 3-1                                                                                                        |

i - 3

## ILLUSTRATIONS

Figure

Title

Page

-

There are no illustrations in this document.

.

TABLES

.

| Table                                                                                | e Title P                                                                                                                 | age  |                                                              |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------|

|                                                                                      | COMPARISON OF PRIME 300 AND PRIME 400 INSTRUCTION<br>EXECUTION TIMES.<br>COMPARISON OF PRIME 300 AND PRIME 400 I/O TIMES. | • •  | 1-4<br>1-5                                                   |

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12<br>2.13 | PRIME 400 ADDRESS CALCULATION FORMATS                                                                                     | •••• | 2-12<br>2-13<br>2-25<br>2-27<br>2-39<br>2-41<br>2-46<br>2-54 |

| 3.1                                                                                  | CONTROL PANEL.                                                                                                            |      | 3–2                                                          |

13 JULY 1976

i - 5

FOREWORD

In the period prior to the publication of the official PRIME 400 System Reference Manual, this document is intended to serve as an interim programmer's reference manual for systems containing the PRIME 400 central processing unit. This document contains the information immediately necessary to allow both systems programmers as well as application programmers to begin utilizing the advanced features of the PRIME 400. As this document discusses only the differences between the PRIME 400 and earlier processors, the reader is expected to have a working familiarity with the PRIME 300.

#### RELATED DOCUMENTS

The following listed documents may provide useful supplemental information to the reader of this User Guide.

| Document Title                          | Order No. |

|-----------------------------------------|-----------|

| Prime 100-200-300 System Reference      | MAN 1671  |

| Macro Assembler User Guide              | MAN 1673  |

| FORTRAN IV User Guide                   | MAN 1674  |

| PRIMOS Interactive User Guide           | MAN 2602  |

| PRIMOS Computer Room User Guide         | MAN 2603  |

| PRIMOS File System User Guide           | MAN 2604  |

| Program Development Software User Guide | MAN 1879  |

## DOCUMENT PRODUCTION

This document was produced on line via the editing and storage features of the Prime PRIMOS operating system. Hard copy suitable for printing has been produced via the RUNOFF command, available with software revision Rev 8.0 of the PRIMOS operating system. User comments, reactions, and suggestions on this document format and content are solicited, as always.

i - 6

## SECTION 1

#### INTRODUCTION

#### 1.1 INTRODUCTION TO THIS DOCUMENT.

In the period prior to the publication of the official PRIME 400 System Reference Manual, this document is intended to serve as an interim programmer's reference manual for systems containing the PRIME 400 central processing unit. This document contains the information immediately necessary to allow both systems programmers as well as application programmers to begin utilizing the advanced features of the PRIME 400. As this document discusses only the differences between the PRIME 400 and earlier processors, the reader is expected to have a working familiarity with the PRIME 300.

This document is provided for information purposes only and is not a specification. All information contained herein is subject to change without notice.

#### 1.2 INTRODUCTION TO THE PRIME 400 PROCESSOR.

The PRIME 400 is a two-board processor designed to plug into the present chassis, to drive all current and planned peripheral devices and controllers, to interface with all present 32K and future memories, to operate all present user-space software, and to obey the compatibility and family constraints of the PRIME Computer User Plan. The processor is very fast (built with high technology) and has segmented addressing (for modern software organization and a very large address space).

Thus, the PRIME 400 does two things. First, it provides a high-end product with the speed and capacity to handle very demanding new applications, such as large data bases, multi-task real-time control, and distributed networks supporting large-scale mainframes. Second, it provides a compatible growth path for existing or proposed PRIME 300 installations. In summary, the PRIME 400 preserves the customer's existing investment in hardware and software while providing a range of new speed and capacity features for greatly enhanced performance in new applications.

#### 1.3 COMPATIBILITY.

Compatibility is a stringent goal in the PRIME 400 product offering. The new processor is absolutely hardware compatible with the present chassis, present power supplies, present 32K memories, all present peripheral device controllers, and the software-visible decor of the PRIME 100/200/300. On the software side, all existing user-space

1 - 1

13 JULY 1976

programming operates without change on the PRIME 400 processor, all present data file structures are preserved without change, and aspects of upward and downward compatibility are maintained.

Notwithstanding the above, certain architectural advantages such as segmentation cannot be downward compatible with respect to programs designed to utilize them effectively. A segmented addressing space provides the basis for a simpler and more effective operating system--a combined DOS, DOS/VM, and RTOS/VM operating system known as PRIMOS. As PRIMOS takes heavy advantage of the advanced features of the PRIME 400 processor, it itself is not downward compatible. However, PRIMOS supports all existing DOS/VM commands, the existing DOS/VM file structures, and all PRIME 100/200/300 addressing and execution modes. Thus all existing user-space programs (including saved memory images) run under PRIMOS without modification. Furthermore, PRIMOS can be used to write, develop, and run new downward-compatible programs which can be interchanged with PRIME 100/200/300 environments at any time.

In one sense then, the management of the downward compatibility of segmentation is handled much the same way as the compatibility of the paging feature of the PRIME 300, which is not available on the PRIME 100/200. That is, an operating system which does take advantage of the feature is provided, which is compatible with previous operating systems, and which allows user-space programs which are indifferent to the feature to be treated in a completely upward- and downward-compatible fashion.

In another sense though, the handling of segmentation is different from the paging feature of the PRIME 300. That is because, in addition to itself taking advantage of the feature, PRIMOS also passes on to the user-space environment the ability to fully utilize segmentation when desired.

#### 1.4 PERFORMANCE.

The PRIME 400 performance is between two and three times that of the PRIME 300, especially in benchmark situations. For comparison, some PRIME 300 and PRIME 400 instruction times are shown in Table 1.1. Note that on the PRIME 300 the ADD instruction in the worst case (which is the usual case) takes 2480 nanoseconds, because of page-translation time (160 ns), 600 ns memory, and the use of relative mode (in which the index operation costs 440 ns). Thus the normal PRIME 300 ADD instruction under DOS/VM takes 2480 ns. By comparison, the best case ADD for the PRIME 400 takes 560 ns, for an improvement factor of 4.4. The comparison of worst to best is fair because on the PRIME 400 the best case is readily achievable in ordinary programming and benchmarks. The average PRIME 400 ADD time (assuming an 85 percent hit rate in the cache and interleaved memories) is 920 ns, which is 2.7 times better than the PRIME 300--a very substantial improvement.

Other integer arithmetic improvements are characterized by the MPY

REV. PRELIM. A

instruction, which improves by 9640/4200 = 2.3 times. Floating-point improvements are characterized by the FAD and FMP instructions, which improve by 8990/4220 = 2.1 times and 25280/9000 = 2.8 times respectively, which are again very substantial savings.

I/O performance is improved in four ways: shorter latency time (the time an I/O controller must wait for service after requesting it); faster data rates (shorter data transfer time when service is granted); many more direct memory access (DMA) channels (in which control information is stored in registers rather than in memory); and entirely new modes (for greater I/O efficiency). Table 1.2 compares the times for the PRIME 300 and PRIME 400 I/O modes.

The architectural features which give these performance improvements are as follows:

- 1. Cache. A 1024-word bipolar buffer between the central processor and memory reduces the effective memory access time from 680 ns to 240 ns. It also eliminates (completely overlaps) the time required for paging and segmentation translation.

- 2. 32-bit arithmetic and logic unit. Arithmetic performed on full 32-bit quantities greatly reduces time for arithmetic and floating-point operations. The 32-bit adder also speeds up relative address formation.

- 3. Faster control unit. The new microcode structure for the control unit allows very fast steps and reduces the number of steps required. For example, a PRIME 400 ADD instruction requires only two steps, as opposed to five on the PRIME 300.

- 4. Registers. The live-register set is increased from 32 16-bit registers on the PRIME 300 to 128 32-bit registers. This allows multiple register sets for very fast process exchange.

- 5. Interleaved memory. On the PRIME 400, main memory can be interleaved, which speeds up sequential access and reduces the cache miss rate.

## TABLE 1.1. COMPARISON OF PRIME 300 AND PRIME 400 INSTRUCTION EXECUTION TIMES.

## PRIME 300 TIMES:

| instruction         | 440 ns mem<br>paging off<br>32S mode | 600 ns mem<br>paging off<br>32S mode | 600 ns mem<br>paging on<br>32S mode | 600 ns mem<br>paging on<br>32R mode |

|---------------------|--------------------------------------|--------------------------------------|-------------------------------------|-------------------------------------|

| ADD M,1             | 1560                                 | 188Ø                                 | 2040                                | 2480                                |

| ADD R<br>(note 1)   | 1760                                 | 1820                                 | 1900                                | 1900                                |

| DAD M,1             | 2800                                 | 328Ø                                 | 3440                                | 3880                                |

| MPY M,1             | 872Ø                                 | 9040                                 | 9200                                | 964Ø                                |

| FAD M,1<br>(note 2) | -                                    | -                                    | -                                   | 8990                                |

| FMP M,1             | -                                    | -                                    | -                                   | +480A+720N<br>25280                 |

## PRIME 400 TIMES:

All times for interleaved 600 ns memories, and include segmentation and paging translation times. The assumed cache hit rate is 85 percent, with a 1200 ns cache fault time (doubleword fetch).

| instruction                    | best case                  | average case               |

|--------------------------------|----------------------------|----------------------------|

| ADD M,1                        | 56Ø                        | 920                        |

| MPY M,1                        | 4200                       | 4560                       |

| FAD M,1<br>(note 1)<br>FMP M,1 | 3500<br>+160A+160N<br>8280 | 4220<br>+160A+160N<br>9000 |

#### ALL TIMES IN NANOSECONDS

NOTE 1: ADD from a register, R<8.

NOTE 2: A = number of required adjust cycles; N = number of required normalization cycles.

REV. PRELIM. A

```

1 - 4

```

| mode                                       | input data<br>transfer time | output data<br>transfer time<br> |

|--------------------------------------------|-----------------------------|----------------------------------|

|                                            |                             |                                  |

| (PRIME 300, 440 ns memory)                 |                             |                                  |

| DMT, first word                            | 276Ø                        | 2600                             |

| DMT, later words                           | 800                         | 880                              |

| DMA, first word                            | 2860                        | 3000                             |

| DMA, later words                           | 1120                        | 1080                             |

| billy facel words                          | 1100                        | 1.000                            |

| DMC, first word                            | 494Ø                        | 498Ø                             |

| DMC, later words                           | 344Ø                        | 3480                             |

| (DDIME 400 DDV DODOVI)                     |                             |                                  |

| (PRIME 400, any memory)<br>DMT, first word | 1400                        | 1640                             |

| DMT, later words                           | 800                         | 880                              |

|                                            | 000                         | 000                              |

| DMA, first word                            | 1400                        | 1640                             |

| DMA, later words                           | 800                         | 88Ø                              |

| DNC first word                             | 2520                        | 2920                             |

| DMC, first word<br>DMC, later words        | 2080                        | 2920                             |

| Dric, racer words                          | 2000                        | 2700                             |

| DMQ                                        | 5000                        | 5000                             |

## TABLE 1.2. COMPARISON OF PRIME 300 AND PRIME 400 I/O TIMES.

## ALL TIMES IN NANOSECONDS

The "first word" times refer to the first word of a block of words to be transferred at the maximum I/O rate. The "later words" times refer to all words of the block after the first word.

## 1.5 INPUT/OUTPUT OPERATION.

Compatibility requires that all PRIME 300 I/O modes be fully supported on the present I/O bus. Thus, I/O through the A-register as well as the DMA, DMC, and DMT direct modes of operation are fully supported, but with improved performance as discussed in Section 1.4. In addition, several new features are added:

- 1. Mapped I/O through segment  $\emptyset$ .

- 2. Remote I/O bus extender and an I/O bus switch.

- 3. New direct-memory queue (DMQ) mode for stream I/O.

- 4. 32 DMA channels instead of 8.

- 5. Very fast DMC data rate.

- 6. Interrupts which automatically initiate process exchange.

The mapped I/O feature allows easy I/O access to the entire 2\*\*22 (4 million) words of physical memory, even though the I/O bus retains its former 18-bit address width. The mapping feature causes I/O accesses to memory to undergo segmentation and paging translation just as processor references; the PRIMOS operating system is responsible for keeping the necessary virtual-to-physical correspondence in effect for the duration of the transfer. This mapping also aids the operating system in performing file transfers.

The remote I/O bus extender allows the addition of up to four remote backplanes, each of which can drive ten I/O controllers, along a 30-foot cable out from the processor. The I/O bus switch allows the switching of controllers among several processors.

A new direct memory queue (DMQ) mode provides a ring-structured memory buffer for the reception and transmission of stream I/O (I/O in which data is transferred in continuous streams of bits, characters, or words, rather than in discrete records). This mode allows the asynchronous multi-line controller to queue messages without the need for extensive software management of "tumble tables" on receive, nor character-time interrupts on transmit. The DMQ mode substantially reduces the PRIMOS overhead in dealing with user-terminal I/O.

The large register set of the PRIME 400 provides for 32 DMA channels. Also, since the cache is used to hold DMC cell pairs, repetitive DMC transfers occur very quickly, as shown in Table 1.2.

For interrupts, a new central processor mode is defined which allows an interrupt signal to be processed as an automatic notify (wakeup) of a process without causing an actual program interruption. The mode automatically issues the proper interrupt-clearing instructions to the signalling controller. This mode allows very fast process exchange times and greatly reduces the overhead of the multiple-priority

REV. PRELIM. A

scheduling schemes common to the RTOS and PRIMOS operating systems.

Overall, PRIME 400 I/O performance is considerably enhanced over the PRIME 300.

#### 1.6 FIRMWARE ENHANCEMENTS.

The PRIME 400 uses a new microcode structure with the following salient features:

- 1. 64-bit microcode word width.

- 2. IBM-style multiway branches.

- 3. 16K words of microcode address space.

- 4. Stack of depth 16.

- 5. Future availability of an extended control storage (XCS) option.

The 64-bit width of the new microcode allows more functions to be controlled in parallel, and thus reduces the number of microcode steps necessary to perform a given function. For example, the ADD instruction executes in two microcode steps on the PRIME 400 as opposed to five steps on the PRIME 300. The IBM-style multiway branches are also important because they are very fast.

The 16K address space allows for considerable future expansion of the microcode. The present two-board PRIME 400 provides 2K 64-bit words of on-board programmable read-only memory (PROM) using 2K PROM parts. However, the board layout will accommodate a 4K PROM part when it becomes available, giving 4K words of on-board PROM.

Microcode can also be expanded with an extended control storage (XCS) board, to be available as an option in the future. The XCS board will provide:

- 1. PROM extension of an additional 2K words (at least).

- 2. 1K words (at least) of program-writable control store.

- 3. Parity checking on all microcode words.

- 4. A simulate mode for writable control store (as in the PRIME 300 writable control storage option).

- 5. A port for connection of a PROM programmer.

The writable control storage will be loaded internally under program control or by I/O operations. The PRIME 400 instruction set has two

addressable and eight generic instructions reserved for a direct decoding into writable control storage. The extended control storage option is being designed specifically to support customer microprograms as well as packaged microcode systems, such as a business instruction set, a fast Fourier transform processor, a matrix operation package, etc.

## 1.7 INTEGRITY ENHANCEMENTS.

The PRIME 400 is equipped with several new integrity features, representing a considerable improvement over the PRIME 300. These features include:

- 1. Parity checking on processor registers and the cache.

- 2. As an option to be available, an error detecting and correcting code on each main memory word.

- 3. Improved program control over the disposition of machine and parity checks.

- 4. Recording of the origin and status of every machine and parity check signal in a diagnostic status word.

- 5. A non-destructive VIRY instruction.

- 6. As an option to be available, a field-engineering panel with a ring-buffer remembering the last 64 microcode addresses fetched by the processor.

Parity is maintained and checked on all the live-registers (128 32-bit registers) of the processor and of the data in the cache. Parity is also checked on all external busses. When the extended control store option is provided, there will also be a parity check on each 64-bit microcode word.

A further option to be available on main memory boards is an error detecting and correcting code on each memory word. The code is capable of correcting all single errors and detecting some double errors. When correction is possible, it is done automatically in the memory on-the-fly, with no delay to the processor. If a correctable error occurs during instruction execution, a check signal which may be requested by the software (see the discussion of the machine check is held off until the completion of the instruction to modes below) allow the computation in progress to benefit from the corrected value; following the check, the operating system can elect to continue the computation regardless of whether or not the hardware or the software elected to run a diagnostic routine in the meanwhile. Correctable errors which occur during direct-memory I/O operation (DMA, DMC, DMT, are simply corrected and cause no check signal ever, to maximize DMO) the likelihood of completing the I/O transfer successfully.

REV. PRELIM. A

$\sum_{i=1}^{n-1} \frac{(a_i + b_i) + a_i + a_i + b_i + b_i}{(a_i + b_i) + b_i} = \sum_{i=1}^{n-1} \frac{(a_i + b_i) + b_i + b_i}{(a_i + b_i) + b_i}$

Uncorrectable errors cause a check signal immediately if during instruction execution, or following completion of the current instruction if during direct-memory I/O, or else are completely ignored (depending upon the machine check mode). As discussed below, all check signals are accompanied by a complete description of the detected error in the diagnostic status word for analysis by the check handler.

The PRIME 400 gives the software improved control over the disposition of check signals. A two-bit machine check mode field is provided which allows the software to run the processor in one of four check modes. The machine check mode field is the last two bits of the processor modals, and is set with the LPSW instruction. The four modes are:

- 00: "None". The processor is not in an error reporting mode. Errors set a program-testable flag but no check is signalled. The diagnostic status word is not set.

- Ø1: "Memory parity". The processor sets the diagnostic status word and generates a check signal for all memory parity errors (and all uncorrectable memory errors detected by the error detecting and correction option, if installed), both during instruction execution and also during direct-memory I/O. Correctable memory errors are ignored and processor parity failures set a program-testable flag in this mode.

- 10: "Quiet". The processor sets the diagnostic status word and generates a check signal for all detected errors other than a correctable memory error. Correctable memory errors are ignored in this mode.

- 11: "Record". The processor sets the diagnostic status word and generates a check signal for all detected errors in this mode. In the case of a correctable memory error, the check signal is held off until the instruction in progress completes, to allow the software the option of resuming the computation following servicing of the check. Correctable memory errors which occur during direct-memory I/O are always ignored, even in this mode, in order to allow the I/O transfer to complete successfully when possible with the correction.

The diagnostic status word is a 96-bit field set by the processor whenever it detects an error which should result in a check signal to the software. The software handling the check signal can read the diagnostic status word to learn the origin of the signal and take appropriate action.

A check is either a memory parity error or else a machine check. There are three circumstances which can cause a memory parity check. The first is detection of a main memory parity error (or an uncorrectable main memory error, if the error detecting and correcting option is installed) during instruction execution when the processor is not in machine check mode ØØ ("none"). The second is occurrence of a correctable main memory error (the error detecting and correcting and correcting and correcting and correcting error between the processor is not in machine check mode ØØ ("none").

1 - 9

13 JULY 1976

option must be installed) during instruction execution when the processor is in machine check mode 11 ("report"). The last is detection of a main memory parity error (or an uncorrectable error, with the correcting option installed) during direct-memory I/O when the processor is not in machine check mode 00 ("none"). When the error detecting and correcting option is installed, corrected errors during I/O execution are always ignored, never set the diagnostic status word, and never signal a check.

MAN2798

A machine check is caused by detection of a parity error on a processor internal register or on an external bus when the processor is in machine check mode 10 ("quiet") or 11 ("record"). When the processor is running in modes 00 ("none") or 01 ("memory parity"), processor parity errors do not set the diagnostic status word and do not cause a check signal, but do set a program-testable flag.

The VIRY instruction triggers a series of microprograms that can verify the integrity of the internal processor components without being destructive to the state of the user's program in execution. This greatly eases restart of the interrupted computation following a check, even if the check handler desires to perform verification.

#### 1.8 IMPLEMENTATION.

The PRIME 400 is implemented as a two-board processor with the boards connected by a 200-signal bus across the top-hat connectors. The top-hat bus carries microcode control signals as well as the full-width source and destination busses for the arithmetic and logic unit (B and D busses). The extended control storage option is packaged as a third board, also connecting via the top-hat bus.

The standard two processor boards hold approximately 330 dual-inline packages each and utilize eight-layer construction. The multilayer construction is used to provide the necessary ground plane for the high-speed logic signals as well as to achieve interconnections at the high package density. The logic family is TTL throughout, mostly Schottky-clamped. No emitter-coupled logic is used. All logic packages are industry standard multiple-sourced units.

REV. PRELIM. A

#### SECTION 2

#### PROGRAM-VISIBLE DECOR

The program-visible portion of the PRIME 400 architecture is described in this section. First, the virtual-memory addressing space (segmentation and paging features) which underlies the PRIME 400 design is discussed. Then, the PRIME 400 instruction and register sets are described in turn. Finally, a number of special features and unique capabilities which contribute to the power of the PRIME 400 product are covered.

#### 2.1 VIRTUAL MEMORY STRUCTURE.

Physical memory on the PRIME 400 can be as large as 4,194,304 (2\*\*22) 16-bit words. The virtual space is 268,435,456 (2\*\*28) 16-bit words. mapping of virtual space to physical space includes both The segmentation and paging. The page size is 1024 words. The segment size is Ø to 65536 words in units of 1024 words. There are 4096 segments to a virtual space. The segments are in four groups of 1024 segments each. There are four descriptor table address registers (DTARs), which point to tables containing segment descriptor words (SDWs), which point to tables containing page map entries (PMNTs), which point to physical pages of memory. Thus a 28-bit virtual address contains 2 bits of descriptor table selection, 10 bits of segment selection, and 16 bits of word selection. It should be noted that the hardware-implemented automatic process-exchange mechanism does not affect the contents of DTARs Ø and 1 and, therefore, all processes share the same first 2048 segments of virtual address space and have the second 2048 segments as private space. Finally, the presence of both paging and segmentation permits the separation of memory management from operating system management. Table 2.1 shows the formats of descriptor table address registers, segment descriptor words, and page map entries.

A descriptor table has from 1 to 1024 entries, must begin on an even word, and must not cross a 65536-word boundary. A page table always has 64 entries and must not cross a 65536-word boundary. Pages must begin on a 1024-word boundary.

There must be no missing memory locations in the first 65536 words of physical memory.

Virtual memory operation is under control of bit 14 of the processor modals, loadable under program control via the LPSW instruction. When this bit is off, no paging or segment translation is performed. The low-order 22 bits of each virtual effective address are taken as a physical address directly.

## TABLE 2.1 VIRTUAL MEMORY FORMATS

# DESCRIPTOR TABLE ADDRESS REGISTER FORMAT (32 bits)

#### SSSSSSSSSSDDDDDD --DDDDDDDDDDDDDDDDD

1-10: 1024 minus descriptor table size (SSS...S).

11-16,

18-32: High-order 21 bits of 22-bit physical address descriptor

17:

table origin, low bit taken as zero (DDD...D). Not used.

7:

## SEGMENT DESCRIPTOR WORD FORMAT (32 bits)

## PPPPPPPPPP------FAAABBBCCCPPPPPP

17: Fault if 1 (F). 18-20: Access allowed t

- Access allowed from ring 1 (AAA).

- 000: No access.

001: Gate (for procedure call).

- ØlØ: Read.

- Øll: Read and write.

- 100, 101: Reserved.

- 110: Read and execute.

- 111: Read, write, and execute.

- 21-23: Reserved for future expansion (BBB).

- 24-26: Access allowed from ring 3, same code as above (CCC).

27-32,

1-10: High-order 16 bits of the 22-bit physical address of the page table origin (PPP...P).

11-16: Reserved, must be zero.

## PAGE MAP ENTRY (16 bits)

#### VRUSAAAAAAAAAAAA

- 1: Valid: page resident if 1, fault if Ø (V).

- 2: Referenced: set by hardware when page is referenced (R).

- 3: Unmodified: reset by hardware when page is modified (U).

- 4: Shared (inhibit usage of cache buffer): set by software when memory page is shared among processors (S).

- 5-16: High-order 12 bits of physical page address, low-order 10 bits are taken as zero (AAA...A).

REV. PRELIM. A

#### 2.2 PRIME 400 INSTRUCTION SET.

For downward compatibility with the PRIME 300, the PRIME 400 provides all of the former addressing modes: 16S, 32S, 32R, and 64R. When running in one of these modes, the PRIME 400 decodes instructions and develops effective addresses in the same way as the PRIME 300. Memory addresses 0 through 7 map onto the live registers in the same way, and the program can directly or indirectly reference up to 65536 words of memory. Support of these four modes allows existing DOS/VM user-space programs to run under the PRIMOS operating system on the PRIME 400 without change. The 16-bit effective addresses generated in the PRIME 300 modes are expanded to a full 28-bit virtual address by automatic concatenation of a 12-bit segment number established when the PRIME 300 mode is entered. Thus, when a DOS/VM user program is run under PRIMOS, its entire 65536-word address space appears as a single segment to the PRIME 400.

To permit usage of multiple segments and the new instructions defined for the PRIME 400, a new virtual-addressing mode is provided: 64V. When run in 64V mode, the PRIME 400 provides access to multiple segments via 32-bit and 48-bit indirect words, four 32-bit base registers, and two 64-bit field address and length registers. In addition, a second index register is provided, and all combinations of base registers, indirection, and pre- and post-indexing by either index register can be specified in instruction addresses.

Instruction decoding in 64V mode proceeds as follows. As in the other modes, sequential decoding begins with bits 3-6 of the instruction word. If these bits are all zero, the instruction is of the generic class, and all the remaining bits of the instruction word are also interpreted as part of the operation code. The PRIME 400 generic instructions include the PRIME 300 generics and many new ones in addition. Table 2.2 lists the PRIME 400 generics and their functions.

If bits 3-6 are not zero, the instruction is of the memory-reference class, bit 7 is the sector bit, S, and bits 8-16 are a displacement, D, in two's complement notation (-256 <= D < +256). If the sector bit is one and the displacement is in the range  $-256 \leq D < -224$ , then instruction word bits 13-14, WW, are interpreted as an extension of the operation code, selecting a column of Table 2.3 for execution. If the sector bit is a zero or the displacement is not in the range  $-256 \leq D < -224$ , then execution occurs from the first column of Table 2.3, as if the extension bits had been zero. Table 2.4 explains the meanings of the memory-reference instructions.

In all memory-reference instructions, bit 1, I, specifies indirect addressing. In all but those with bits 3-6 equal to 1101, bit 2, X, specifies indexing. When bits 3-6 equal 1101, bit 2 is used as an extension of the operation code, and such instructions cannot be indexed.

# TABLE 2.2.

## PRIME 400 GENERIC INSTRUCTIONS.

This table summarizes all PRIME 400 generic operations, grouped by function. Instructions marked "RESTRICTED" can be executed only in ring zero. Rings are discussed in Section 2.3.

The "type" column indicates the format and/or function of the operation as follows.

AP: Three-word operation, the last two words of which are an AP address pointer.

BR: Two-word operation, the second word of which is a word number within the current procedure segment to which to branch.

- CON: Single-word control operation.

- FLD: Single-word field operation.

FOPR: Single-word floating-point operation.

FSKP: Single-word floating-point skip operation.

IG: Single-word integrity operation.

IO: Single-word input/output operation.

LOG: Single-word logicize operation.

MODE: Single-word mode operation.

OPR: Single-word miscellaneous operation.

SH: Single-word shift operation.

SKP: Single-word skip operation.

The "C" column indicates the effect of the operation on the C-bit and the L-bit as follows.

-: C and L are unchanged by the operation.

1: C is unchanged, L is carry.

- 2: C is overflow, L is carry.

- 3: C is overflow, L is indeterminant.

4: C is shift extension, L is indeterminant.

5: C is a result of the operation, L is indeterminant.

6: C and L are indeterminant.

7: C and L are loaded by the operation.

8: C is cleared, L is indeterminant.

The "cc" column indicates the effect of the operation on the condition codes as follows.

- -: Condition codes are unchanged by the operation.

- 1,4: Condition codes indicate the result of the arithmetic operation or compare.

- 5: Condition codes are indeterminant.

6: Condition codes are loaded by the operation.

7: Condition codes indicate the result of the operation.

mnem opcode type C cc description

(MISCELLANEOUS AP OPERATIONS.)

| WAIT  | 000315 | AP    | -    | -             | WAIT ON SEMAPHORE AT AP. RESTRICTED.                                         |

|-------|--------|-------|------|---------------|------------------------------------------------------------------------------|

| CALF  | 000705 | AP    | 7    | 6             | PROCEDURE CALL FROM FAULTING PROC. TO FAULT HANDLER.                         |

| LPSW  | ØØØ711 | AP    | 7    | 6             | LOAD PROGRAM STATUS WORD (SEGN, WORDN, KEYS, MODALS). RESTRICTED.            |

| RSAV  | 000715 | AP    | -    | -             | SAVE REGISTERS (GENERAL, FLOATING, TEMPORARY<br>BASE) :                      |

| RRST  | ØØØ717 | AP    | -    | -             | RESTORE REGISTERS (GENERAL, FLOATING, TEMPORARY                              |

| STAC  | 001200 | AP    | -    | 7             | BASE).<br>STORE A CONDITIONAL ON B=[EA16]. CCEQ= SUCCESS                     |

| STLC  | ØØ12Ø4 | AP    | -    | 7             | ELSE FAIL.<br>STORE L CONDITIONAL ON E=[EA32]. CCEQ= SUCCESS                 |

| NFYE  | ØØ121Ø | AP    | 6    | 5             | ELSE FAIL.<br>NOTIFY ON SEMAPHORE AT AP. USE FIFO QUEUEING.                  |

| NFYB  | ØØ1211 | AP    | 6    | 5             | NO CAI. RESTRICTED.<br>NOTIFY ON SEMAPHORE AT AP. USE LIFO QUEUEING.         |

| INEN  | ØØ1214 | AP    | 6    | 5             | NO CAI. RESTRICTED.<br>NOTIFY DURING INTERRUPT CODE. USE FIFO                |

| INBN  | ØØ1215 | AP    | 6    | 5             | QUEUEING. NO CAI. RESTRICTED.<br>NOTIFY DURING INTERRUPT CODE. USE LIFO      |

| INEC  | ØØ1216 | AP    | 6    | 5             | QUEUEING. NO CAI. RESTRICTED.<br>NOTIFY DURING INTERRUPT CODE. USE FIFO      |

| INBC  | ØØ1217 | AP    | 6    | 5             | QUEUEING. DO CAI. RESTRICTED.<br>NOTIFY DURING INTERRUPT CODE. USE LIFO      |

| RTQ   | 141714 | AP    | -    | 6             | QUEUEING. DO CAI. RESTRICTED.<br>REMOVE FROM TOP OF QUEUE. ON EMPTY, A=Ø AND |

| RBQ , | 141715 | AP    | -    | 6             | CC'S SET EQ.<br>REMOVE FROM BOTTOM OF QUEUE. ON EMPTY, A=Ø AND               |

| ABQ   | 141716 | AP    | -    | 6             | CC'S SET EQ.<br>ADD TO BOTTOM OF QUEUE. CCEQ = FULL ELSE NOT                 |

| ATQ   | 141717 | AP    | -    | 6             | FULL.<br>ADD TO TOP OF QUEUE. CCEQ = FULL ELSE NOT                           |

| TSTQ  | 141757 | AP    | -    | 6             | FULL.<br>TEST QUEUE. A SET TO # ITEMS IN QUEUE. CC'S<br>SET EQ ON EMPTY.     |

| (BRAI | CH OPE | RATIO | NS.) | I             |                                                                              |

| BLE   | 140610 | BR    | _    | 4             | BRANCH ON A REGISTER .LE. Ø.                                                 |

| BGT   | 140611 |       | _    | 4             | BRANCH ON A REGISTER .GT. Ø.                                                 |

| BEQ   | 140612 |       | -    | 4             | BRANCH ON A REGISTER .EQ. Ø.                                                 |

| BNE   | 140613 |       | _    | $\frac{1}{4}$ | BRANCH ON A REGISTER .NE. Ø.                                                 |

| BLT   | 140614 |       |      | 4             | BRANCH ON A REGISTER .LT. Ø.                                                 |

|       | 140614 |       | _    | 4             | BRANCH ON L REGISTER .LT. Ø.                                                 |

|       | 140614 |       | _    | 4<br>4        | BRANCH ON L REGISTER . GE. Ø.                                                |

|       |        |       |      |               |                                                                              |

| BGE   | 140615 |       | _    | 4<br>4        | BRANCH ON A REGISTER .GE. Ø.<br>BRANCH ON L REGISTER .LE. Ø.                 |

| 머니니다  | 140700 | DK    | -    | 4             | DRAINCH UN LI REGIDIER .LE. V.                                               |

BLGT 140701 BR - 4 BRANCH ON L REGISTER .GT. 0.

•

2 - 5

13 JULY 1976

..

r

-

| BLEQ  | 140702           | BR    | -   | 4  | BRANCH ON L REGISTER .EQ. Ø.<br>BRANCH ON L REGISTER .NE. Ø.                                                                                              |

|-------|------------------|-------|-----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLNE  | 140703           | BR    | _   | 4  | BRANCH ON L REGISTER NE. Ø.                                                                                                                               |

| BDY   | 140724           | BR    |     |    | BRANCH ON DECREMENTED Y.                                                                                                                                  |

| BDX   | 140734           | BR    | _   | _  | BRANCH ON DECREMENTED X.                                                                                                                                  |

| BIY   | 140734<br>141324 | BR    | _   | _  | BRANCH ON INCREMENTED Y.                                                                                                                                  |

| BIX   | 141334           | BR    | _   | _  | BRANCH ON INCREMENTED X.                                                                                                                                  |

|       | 141600           |       |     |    | BRANCH ON CONDITION CODE .LE.                                                                                                                             |

|       | 141601           |       |     |    | BRANCH ON CONDITION CODE .GT.                                                                                                                             |

|       | 141602           |       |     |    | BRANCH ON MAGNITUDE-CONDITIONS L,CC .EQ.                                                                                                                  |

|       | 141602           |       |     |    | BRANCH ON CONDITION CODE .EQ.                                                                                                                             |

|       | 141603           |       |     |    | BRANCH ON CONDITION CODE .NE.                                                                                                                             |

|       |                  |       |     |    | BRANCH ON MAGNITUDE-CONDITIONS L, CC .NE.                                                                                                                 |

| BCS   | 141604           | BR    | _   |    | BRANCH ON CBIT SET.                                                                                                                                       |

|       |                  |       |     |    | BRANCH ON CONDITION CODE .GE.                                                                                                                             |

|       | 141610           |       |     |    |                                                                                                                                                           |

|       | 141611           |       |     |    | BRANCH ON FLOATING ACCUMULATOR .LE. Ø.<br>BRANCH ON FLOATING ACCUMULATOR .GT. Ø.                                                                          |

|       | 141612           |       |     |    |                                                                                                                                                           |

|       | 141612           |       |     |    | BRANCH ON FLOATING ACCUMULATOR .EQ. Ø.                                                                                                                    |

|       |                  |       |     |    | BRANCH ON FLOATING ACCUMULATOR .NE. Ø.                                                                                                                    |

|       | 141614           |       |     |    | BRANCH ON FLOATING ACCUMULATOR .LT. Ø.                                                                                                                    |

|       | 141615           |       |     | 4  | BRANCH ON FLOATING ACCUMULATOR .GE. Ø.                                                                                                                    |

|       | 141704           |       |     |    | BRANCH ON CONDITION CODE .LT.                                                                                                                             |

|       | 141705           |       |     |    | BRANCH ON CBIT RESET.                                                                                                                                     |

| BMGE  | 141/06           | BR    | -   | -  | BRANCH ON MAGNITUDE-CONDITIONS L,CC .GE.                                                                                                                  |

| BLS   | 141/06           | BR    | -   | -  | BRANCH ON LINK SET.                                                                                                                                       |

| BLR   | 141707           | BR    | -   | -  | BRANCH ON LINK RESET.                                                                                                                                     |

| BMLT  | 141707           | BR    | -   | -  | BRANCH ON MAGNITUDE-CONDITIONS L,CC .LT.                                                                                                                  |

| BMGT  | 141710           | BR    |     | -  | BRANCH ON MAGNITUDE-CONDITIONS L,CC .GT.                                                                                                                  |

| BMLE  | 141711           | BR    | -   |    | BRANCH ON LINK RESET.<br>BRANCH ON MAGNITUDE-CONDITIONS L,CC .LT.<br>BRANCH ON MAGNITUDE-CONDITIONS L,CC .GT.<br>BRANCH ON MAGNITUDE-CONDITIONS L,CC .LE. |

|       |                  |       |     |    |                                                                                                                                                           |

| (CON  | FROL OPH         | ERATI | ONS | .) |                                                                                                                                                           |

|       |                  |       |     |    |                                                                                                                                                           |

| HLT   |                  |       |     |    | HALT COMPUTER OPERATION. RESTRICTED.                                                                                                                      |

| SVC   |                  |       |     |    | SUPERVISOR CALL.                                                                                                                                          |

| IRTN  | 000601           | CON   | 7   | 6  | INTERRUPT RETURN, NO CAI. RESTRICTED.                                                                                                                     |

| IRTC  | 000603           | CON   | 7   | 6  | INTERRUPT RETURN, DO CAI. RESTRICTED.                                                                                                                     |

| ARGT  | 000605           | CON   | _   | -  | ARGUMENT TRANSFER (USED WITH PCL).                                                                                                                        |

| PRTN  | 000611           | CON   | 7   | 6  | PROCEDURE RETURN.                                                                                                                                         |

| ITLB  | 000615           | CON   | _   |    | INVALIDATE STLB ENTRY, L HAS VIRTUAL ADDRESS.                                                                                                             |

|       |                  |       |     |    | RESTRICTED.                                                                                                                                               |

| LPID  | 000617           | CON   | _   | -  | LOAD PROCESS ID FROM A01-A12. RESTRICTED.                                                                                                                 |

| CGT   | ØØ1314           | -     | 6   | 5  | LOAD PROCESS ID FROM A01-A12. RESTRICTED.<br>COMPUTED GO TO.                                                                                              |

|       |                  |       |     |    |                                                                                                                                                           |

| (FIE  | LD OPERA         | TION  | s.) |    |                                                                                                                                                           |

|       |                  |       |     |    |                                                                                                                                                           |

| EAFA  | ØØ13ØØ           | AP    |     |    | EFFECTIVE ADDRESS TO FIELD REGISTER ZERO.                                                                                                                 |

|       | 001301           |       |     | 5  | ADD L TO FIELD ADDRESS REGISTER ZERO.                                                                                                                     |

|       | 001302           |       |     |    | LOAD CHAR TO A REG. AS SPECIFIED BY FIELD                                                                                                                 |

|       |                  |       |     | -  | ADDRESS REG. ZERO.                                                                                                                                        |

| LFT.T | 001303           | _     | _   | _  | LOAD FIELD LENGTH REGISTER IMMEDIATE ZERO.                                                                                                                |

|       | ØØ131Ø           |       | _   | _  | EFFECTIVE ADDRESS TO FIELD REGISTER ONE.                                                                                                                  |

|       |                  |       |     |    | ADD L TO FIELD ADDRESS REGISTER ONE.                                                                                                                      |

|       |                  |       | n   |    |                                                                                                                                                           |

| T.M   |                  |       |     |    |                                                                                                                                                           |

| LDC   | 001311<br>001312 |       |     |    | LOAD CHAR TO A REG. AS SPECIFIED BY FIELD                                                                                                                 |

| LDC   |                  |       |     |    |                                                                                                                                                           |

REV. PRELIM. A

LFLI ØØ1313 - - - LOAD FIELD LENGTH REGISTER IMMEDIATE ONE. STFA 001320 AP - - STORE FIELD ADDRESS REGISTER ZERO. TLFL 001321 FLD - - TRANSFER L TO FIELD LENGTH REGISTER ZERO. STC 001322 FLD - 7 STORE CHAR FROM A REG. AS SPECIFIED BY FIELD ADDRESS REG. ZERO. TRANSFER FIELD LENGTH REG. TO L REG. ZERO. TFLL ØØ1323 FLD - -STFA ØØ1330 AP--STORE FIELD ADDRESS REGISTER ONE.TLFL ØØ1331 FLD--TRANSFER L TO FIELD LENGTH REGISTER ONE.STC ØØ1332 FLD-7STORE CHAR FROM A REG. AS SPECIFIED BY FIELD ADDRESS REG. ONE. TFLL 001333 FLD - - TRANSFER FIELD LENGTH REG. TO L REG. ONE. (FLOATING-POINT OPERATIONS.) CONVERT SINGLE FLOATING TO DOUBLE FLOATING. FDBL 140016 FOPR - -FAC=>DFAC. FCM 140530 FOPR 3 5 FLOATING COMPLEMENT. -FAC=>FAC. CONVERT FLOATING TO INTEGER. INT(FAC) =>A. INTA 140531 FOPR 3 5 FLTA 140532 FOPR 3 5 INTL 140533 FOPR 3 5 FRN 140534 FOPR 3 5 FLOATING ROUND UP. CONVERT INTEGER TO FLOATING. FLOT(A)=>FAC. CONVERT FLOATING TO LONG INTEGER. INT(FAC) =>L. CONVERT LONG INTEGER TO FLOATING. FLTL 140535 FOPR 8 5 FLOT(L) = > FAC. CONVERT DP INTEGER WITH HOLE TO FLOATING. FLOT 140550 FOPR 6 5 FLOT(A,B) = >FAC.CONVERT FLOATING TO DP INTEGER WITH HOLE. INT 140554 FOPR 3 5 INT(FAC) = >A, B.DOUBLE FLOATING COMPLEMENT. -DFAC=>DFAC. DFCM 140574 FOPR 3 5 (FLOATING-POINT SKIP OPERATIONS.) FSZE 140510 FSKP - 4 FLOATING SKIP IF .EQ. 0. FSNZ 140511 FSKP - 4 FLOATING SKIP IF .NE. 0. FSMI 140512 FSKP - 4 FLOATING SKIP IF .LT. Ø. FSPL 140513 FSKP - 4 FLOATING SKIP IF .GE. Ø. FSLE 140514 FSKP - 4 FLOATING SKIP IF .LE. Ø. FSGT 140515 FSKP - 4 FLOATING SKIP IF .GT. 0. (INTEGRITY OPERATIONS.) RESET MACHINE CHECK FLAG. RESTRICTED. RMC 000021 IG - -VIRY 000311 IG 5 6 EXECUTE VERIFICATON ROUTINE. RESTRICTED. LMCM 000501 IG - - LEAVE MACHINE CHECK MODE. RESTRICTED. ENTER MACHINE CHECK MODE. RESTRICTED. EMCM 000503 IG - -MEMORY DIAGNOSTIC ENABLE INTERLEAVE. MDEI ØØ1304 IG - -RESTRICTED. MDII 001305 IG - -MEMORY DIAGNOSTIC INHIBIT INTERLEAVE. RESTRICTED. MDRS 001306 IG - - MEMORY DIAGNOSTIC READ SYNDROME BITS. RESTRICTED. MDWC 001307 IG - - MEMORY DIAGNOSTIC LOAD WRITE CONTROL REGISTER. RESTRICTED.

2 - 7

13 JULY 1976

••

ખ

.

| MDIW     | 0013??  | IG    | _    | -     | MEMORY DIAGNOSTIC WRITE INTERLEAVED. L=>[E].<br>RESTRICTED.                                 |

|----------|---------|-------|------|-------|---------------------------------------------------------------------------------------------|

| (INP     | UT/OUTP | UT OF | PERA | NTION | NS.)                                                                                        |

| ENB      | 000401  | IO    | _    |       | ENABLE INTERRUPTS. RESTRICTED.                                                              |

| CAI      |         |       |      |       | CLEAR ACTIVE INTERRUPT. RESTRICTED.                                                         |

| INH      | 001001  | IO    | -    | -     | INHIBIT INTERRUPTS. RESTRICTED.                                                             |

| (LOG     | ICIZE O | PERAI | ION  | IS.)  |                                                                                             |

| LLT      | 140410  | LOG   | -    | 4     | LOGICIZE ON A REG. LT. IF A.LT. $\emptyset$ , 1=>A<br>ELSE $\emptyset$ =>A.                 |

| LLLT     | 140410  | LOG   | -    | 4     |                                                                                             |

| LLE      | 140411  | LOG   | -    | 4     |                                                                                             |

| LNE      | 140412  | LOG   | -    | 4     | LOGICIZE ON A REG. NE. IF A.NE.Ø, 1=>A                                                      |

| LEQ      | 140413  | LOG   | -    | 4     |                                                                                             |

| LGE      | 140414  | LOG   | -    | 4     |                                                                                             |

| LLGE     | 140414  | LOG   | -    | 4     |                                                                                             |

| LGT      | 140415  | LOG   | _    | 4     | ELSE Ø=>A.<br>LOGICIZE ON A REG. GT. IF A.GT.Ø, 1=>A                                        |

|          |         |       |      |       | ELSE Ø=>A.                                                                                  |

|          | 140416  |       |      |       |                                                                                             |

|          | 140417  |       |      |       |                                                                                             |

| LF, L'L, | 141110  | LOG   | -    | 4     | LOGICIZE ON FLOATING LT. IF FAC.LT.0, $1 \Rightarrow A$<br>ELSE $0 \Rightarrow A$ .         |

| LFLE     | 141111  | LOG   | -    | 4     | LOGICIZE ON FLOATING LE. IF FAC.LE.0, $1 \Rightarrow A$<br>ELSE $\emptyset \Rightarrow A$ . |

| LFNE     | 141112  | LOG   | -    | 4     | LOGICIZE ON FLOATING NE. IF FAC.NE. $\emptyset$ , 1=>A<br>ELSE $\emptyset$ =>A.             |

| LFEQ     | 141113  | LOG   | -    | 4     | LOGICIZE ON FLOATING EQ. IF FAC.EQ. $\emptyset$ , 1=>A<br>ELSE $\emptyset$ =>A.             |

| LFGE     | 141114  | LOG   | -    | 4     | LOGICIZE ON FLOATING GE. IF FAC.GE.0, $1=>A$<br>ELSE $\emptyset =>A$ .                      |

| LFGT     | 141115  | LOG   | -    | 4     | LOGICIZE ON FLOATING GT. IF FAC.GT. $\emptyset$ , 1=>A                                      |

| LCLT     | 141500  | LOG   | -    | -     | ELSE Ø=>A.<br>LOGICIZE ON COND CODE LT. IF CC.LT.,1=>A                                      |

| LCLE     | 141501  | LOG   | -    |       | ELSE Ø=>A.<br>LOGICIZE ON COND CODE LE. IF CC.LE.,1=>A                                      |

| LCNE     | 141502  | LOG   | -    | -     | ELSE Ø=>A.<br>LOGICIZE ON COND CODE NE. IF CC.NE.,1=>A                                      |

| LCEQ     | 141503  | LOG   | -    | -     | ELSE Ø=>A.<br>LOGICIZE ON COND CODE EQ. IF CC.EQ.,1=>A                                      |

| TOOD     | 141594  | T 00  |      |       | ELSE $\emptyset = >A$ .                                                                     |

|          | 141504  |       |      |       | LOGICIZE ON COND CODE GE. IF CC.GE., $1 \Rightarrow A$<br>ELSE $\emptyset \Rightarrow A$ .  |

| LCGT     | 141505  | LOG   |      | -     | LOGICIZE ON COND CODE GT. IF CC.GT., $1 \Rightarrow A$<br>ELSE $\emptyset \Rightarrow A$ .  |

.

LOGICIZE ON L REG. LE. IF L.LE.Ø, 1=>A LLLE 141511 LOG - 4 ELSE  $\emptyset = >A$ . LOGICIZE ON L REG. NE. IF L.NE.Ø,  $1 \Rightarrow A$ LLNE 141512 LOG - 4 ELSE  $\emptyset = >A$ . LLEO 141513 LOG - 4 LOGICIZE ON L REG. EQ. IF L.EQ.0, 1 = > AELSE  $\emptyset = >A$ . LLGT 141515 LOG - 4 LOGICIZE ON L REG. GT. IF L.GT. $\emptyset$ , 1=>A ELSE  $\emptyset = >A$ . (MODE OPERATIONS.) SGL 000005 MODE - -ENTER SINGLE-PRECISION MODE. ENTER DOUBLE-PRECISION MODE (NOT USEFUL IN DBL 000007 MODE - -64V MODE). E64V 000010 MODE - - ENTER P400 MODE. E16S ØØØØ11 MODE – – ENTER P3ØØ 16K SECTORED MODE. E32S ØØØØ13 MODE – – ENTER P3ØØ 32K SECTORED MODE. ESIM 000415 MODE - - ENTER STANDARD INTERRUPT MODE. RESTRICTED. EVIM 000417 MODE - - ENTER VECTORED INTERUPT MODE. RESTRICTED. E64R ØØ1Ø11 MODE – – ENTER P3ØØ 64K RELATIVE MODE. E32R ØØ1Ø13 MODE – – ENTER P3ØØ 32K RELATIVE MODE. (MISCELLANEOUS OPERATIONS.) NOP 000001 OPR - -NO OPERATION. LONG INTEGER TO SHORT INTEGER CONVERSION. PIMA ØØØØ15 OPR 3 5 L=>A. IEX ON PRECISION LOSS. SCA 000041 OPR - -LOAD P-300 SHIFT COUNTER INTO A REG. INPUT P-300 KEYS INTO A REG. INK ØØØØ43 OPR - -NRM 000101 OPR - -NORMALIZE A, B AS ON P-300 (NOT USEFUL IN 64V MODE). RETURN FROM P-300 RECURSIVE PROCEDURE (NOT RTN ØØØ1Ø5 OPR - -USEFUL IN 64V MODE). CALCULATE EFFECTIVE ADDRESS. A AS EA=>A. (NOT CEA ØØØ111 OPR - -USEFUL IN 64V MODE.) SHORT INTEGER TO LONG INTEGER CONVERSION. PIDA 000115 OPR - -A=>L. IAB ØØØ2Ø1 OPR - -INTERCHANGE A REG. WITH B REG. A=>B & B=>A. PIM 000205 OPR - -CONVERT DP INTEGER WITH HOLE TO SHORT INTEGER. PID ØØØ211 OPR - - CONVERT SHORT INTEGER TO DP INTEGER WITH HOLE. PIML 000301 OPR 3 5 CONVERT 64BIT INTEGER TO LONG INTEGER. (L,E) =>L.PIDL 000305 OPR - -CONVERT LONG INTEGER TO 64 BIT INTEGER. OTK 000405 OPR 7 6 OUTPUT A REG. TO P-300 KEYS AND SHIFT COUNTER. TKA ØØ1ØØ5 OPR - - TRANSFER KEYS TO A. TAK ØØ1Ø15 OPR 7 6 TRANSFER A TO KEYS. STEX ØØ1315 OPR 6 5 STACK EXTEND. L REG. HAS EXTENT. WCS ENTRANCES. UII ON NO WCS OR WCS NOT LOADED. MAY BE MICROPROGRAMMED TO BE RESTRICTED. CRL 140010 OPR - - CLEAR L REGISTER. 0=>L.

|      | 140014   | OPR  | -   | - | Obsolete. Clears both the B-register and the least-significant word of the DFAC. See Section 2.8. |

|------|----------|------|-----|---|---------------------------------------------------------------------------------------------------|

| CRB  | 140015   | OPR  | _   | _ | CLEAR B REGISTER. Ø=>B.                                                                           |

| CHS  | 140024   |      |     | - | CHANGE SIGN OF A REGISTER.                                                                        |

| CRA  | 140040   |      |     | - | CLEAR A REGISTER. $\emptyset => A$ .                                                              |

| SSP  | 140100   |      |     |   |                                                                                                   |

| XCA  | 140104   |      |     | - |                                                                                                   |

| SIA  | 140110   |      |     |   | SUBTRACT 1 FROM A REGISTER. $A-1=>A$ .                                                            |

| IRX  | 140114   |      |     |   |                                                                                                   |

| RCB  | 140200   |      |     |   |                                                                                                   |

|      | 140200   |      |     | _ |                                                                                                   |

|      | 140210   |      |     |   |                                                                                                   |

| CAZ  | 140210   |      |     |   |                                                                                                   |

| CAL  |          |      |     | Ŧ | >,=,< Ø.                                                                                          |

| A2A  | 140304   |      |     | 1 | ADD 2 TO A REGISTER. A+2=>A.                                                                      |

| S2A  | 140310   | OPR  | 2   | 1 | SUBTRACT 2 FROM A REGISTER. A-2=>A.                                                               |

| TAB  | 140314   | OPR  | -   | - | TRANSFER A TO B REG. A=>B.                                                                        |

| CSA  | 140320   | OPR  | 5   |   | COPY SIGN OF A. Al=>CBIT, $\emptyset$ =>Al.                                                       |

| CMA  | 140401   | OPR  | -   | - | ONE'S COMPLEMENT A REGISTER.                                                                      |

| TCA  | 140407   | OPR  | 2   | 1 | TWO'S COMPLEMENT A REGISTERA=>A.                                                                  |

| SSM  | 140500   | OPR  | _   | - | SET SIGN OF A REG. MINUS. 1=>A1.                                                                  |

| TAX  | 140504   | OPR  | _   |   | TRANSFER A REG. TO X REG. A=>X.                                                                   |

| TAY  | 140505   | OPR  | _   | _ | TRANSFER A REG. TO Y REG. A=>Y.                                                                   |

| SCB  | 140600   | OPR  | 5   | _ | SET CBIT. 1=>CBIT.                                                                                |

| TBA  | 140604   |      |     |   | TRANSFER B REG. TO A REG. B=>A.                                                                   |

| ADLL | 141000   |      |     | 1 | ADD LINK TO L REGISTER.                                                                           |

|      | 141034   |      |     | _ | TRANSFER X REG. TO A REG. $X = >A$ .                                                              |

|      | 141044   |      |     | _ | CLEAR A REG. RIGHT BYTE.                                                                          |

|      | 141050   |      |     |   | CLEAR A REG. LEFT BYTE.                                                                           |

| TYA  |          |      |     |   | TRANSFER Y REG. TO A REG. Y=>A.                                                                   |

| ICL  | 141140   |      |     | - | INTERCHANGE BYTES OF A REG. AND CLEAR LEFT<br>BYTE.                                               |

| AlA  | 1412Ø6   | OPR  | 2   | 1 | ADD 1 TO A REG. $A+1=>A$ .                                                                        |

| TCL  | 141210   |      |     | ī | TWO'S COMPLEMENT L. $-L=>L$ .                                                                     |

| ACA  | 141216   |      |     | ī | ADD CBIT TO A REG. CBIT+ $A=>A$ .                                                                 |

| ICR  | 141240   |      | -   | _ | INTERCHANGE BYTES OF A REG. AND CLEAR RIGHT                                                       |

|      |          |      |     |   | BYTE.                                                                                             |

| ICA  | 141340   | OPR  | -   |   | INTERCHANGE BYTES OF A REG.                                                                       |

| CRE  | 141404   | OPR  | -   | - | CLEAR E. Ø=>E.                                                                                    |

| CRLE | 141410   | OPR  | _   | - | CLEAR L AND E. $\emptyset = >L, \emptyset = >E$ .                                                 |

| ILE  | 141414   | OPR  | -   | - | INTERCHANGE L AND E. L=>E & E=>L.                                                                 |

| (SHI | FT OPERA | TION | s.) |   |                                                                                                   |

| LRL  | Ø4ØØXX   | SH   | 4   | 5 | LONG RIGHT LOGICAL.                                                                               |

|      | Ø401XX   |      |     | 5 | LONG RIGHT SHIFT (LONG INTEGER ARITHMETIC IN                                                      |

|      |          |      | -   | - | 64V MODE, ELSE DP INTEGER WITH HOLE).                                                             |

| LRR  | Ø4Ø2XX   | SH   | 4   | 5 | LONG RIGHT ROTATE.                                                                                |

| ARL  | Ø4Ø4XX   | SH   | 4   | 5 | A RIGHT LOGICAL.                                                                                  |

|      | Ø4Ø5XX   |      |     |   | A RIGHT SHIFT (SHORT INTEGER ARITHMETIC).                                                         |

|      | Ø4Ø6XX   |      |     |   | A RIGHT ROTATE.                                                                                   |

|      | Ø410XX   |      |     |   | LONG LEFT LOGICAL.                                                                                |

|      | ~        |      | I   | 5 | Pous TELI INGIONE.                                                                                |

REV. PRELIM. A

LONG LEFT SHIFT (LONG INTEGER ARITHMETIC IN 64V LLS Ø411XX SH 4 5 MODE, ELSE DP. INTEGER WITH HOLE). LLR Ø412XX SH 4 5 LONG LEFT ROTATE. ALL Ø414XX SH 4 5 A LEFT LOGICAL. 4 5 A LEFT SHIFT (SHORT INTEGER ARITHMETIC). ALS Ø415XX SH 4 5 A LEFT ROTATE. ALR Ø416XX SH (SKIP OPERATIONS.) SKP 100000 SKP - - SKIP ONE WORD. SRC 100001 SKP - - SKIP IF CBIT RESET. SR4 100002 SKP - - SKIP IF SENSE SWITCH 4 RESET. RESTRICTED. SR3 100004 SKP - - SKIP IF SENSE SWITCH 3 RESET. RESTRICTED. SR2 100010 SKP - - SKIP IF SENSE SWITCH 2 RESET. RESTRICTED. SR1 100020 SKP - - SKIP IF SENSE SWITCH 1 RESET. RESTRICTED. SSR 100036 SKP - - SKIP IF SENSE SWITCHES 1,2,3 AND 4 RESET. RESTRICTED. SZE 100040 SKP - - SKIP IF A REG. .EO. 0. SLZ 100100 SKP - - SKIP IF A REG. BIT 16 .EQ. 0. SMCR 100200 SKP - - SKIP IF MACHINE CHECK RESET. SGT 100220 SKP - - SKIP IF A REG. .GT. 0. SNR 10024X SKP - - SKIP IF SENSE SWITCH N RESET. RESTRICTED. SAR 10026X SKP - - SKIP IF A REG. BIT N RESET. SPL 100400 SKP - - SKIP IF A REG. .GE. 0. SSC 101001 SKP - - SKIP IF CBIT SET. SS4 101002 SKP - - SKIP IF SENSE SWITCH 4 SET. RESTRICTED. SS3 101004 SKP - - SKIP IF SENSE SWITCH 3 SET. RESTRICTED. SS2 101010 SKP - - SKIP IF SENSE SWITCH 2 SET. RESTRICTED. SS1 101020 SKP - -SKIP IF SENSE SWITCH 1 SET. RESTRICTED. SSS 101036 SKP - -SKIP IF SENSE SWITCHES 1,2,3 AND 4 SET. RESTRICTED. SNZ 101040 SKP - - SKIP IF A REG. NE. 0. SLN 101100 SKP - - SKIP IF A REG. BIT 16 SET. SMCS 101200 SKP - - SKIP IF MACHINE CHECK SET. SLE 101220 SKP - - SKIP IF A REG. .LE. 0. SNS 101240 SKP - - SKIP IF SENSE SWITCH N SET. RESTRICTED. SAS 101260 SKP - - SKIP IF A REG. BIT N SET. SMI 101400 SKP - - SKIP IF A REG. .LT. 0.

|                                                                                                        |                                                                                                       | instruction<br>(if S=1 and                                                                     | bits 13-14<br>-256<=D<-224)<br>                                                                |                                                              |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| instruction<br>bits 3-6                                                                                | ØØ                                                                                                    | Ø1<br>                                                                                         | 10                                                                                             | 11                                                           |

| 0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010<br>1001<br>1101*<br>1101* | JMP<br>LDA<br>ANA<br>STA<br>ERA<br>ADD<br>SUB<br>JST<br>CAS<br>IRS<br>IRS<br>IMA<br>JSY<br>STX<br>LDX | EAL<br>FLD<br>STLR<br>FST<br>LDLR<br>FAD<br>FSB<br>-<br>FCS<br>MIA<br>MIB<br>EIO<br>FLX<br>LDY | XEC<br>DFLD<br>ORA<br>DFST<br>-<br>DFAD<br>DFSB<br>PCL<br>DFCS<br>EAXB<br>EALB<br>JSXB<br>DFLX | _<br>LDL<br>ANL<br>STL<br>ERL<br>ADL<br>SBL<br>_<br>CLS<br>_ |

| 1110<br>1110<br>1111                                                                                   | MPY<br>DIV                                                                                            | EDY<br>FMP<br>FDV                                                                              | STY<br>DFMP<br>DFDV                                                                            | JSX<br>MPL<br>DVL                                            |

## TABLE 2.3. PRIME 400 MEMORY-REFERENCE INSTRUCTIONS (WHEN IN 64V MODE).

Use column 00 if S (bit 7) is 0 or if D (bits 8-16) is not in the range -256 <= D < -224.

.

- \*: Use this row if bit 2 of the instruction word is a zero. These instructions cannot be indexed.

- \*\*: Use this row if bit 2 of the instruction word is a one. These instructions cannot be indexed.

## TABLE 2.4.

## PRIME 400 MEMORY-REFERENCE INSTRUCTION DESCRIPTIONS.

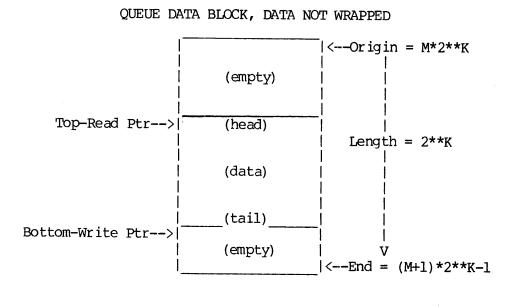

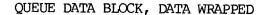

This list summarizes all PRIME 400 memory-reference and programmed input/output instructions, sorted by operation code. The first number in the "opcode" column is the octal representation of instruction bits 3-6. The second number is the octal representation of bits 13-14 (bits 13-14 are inspected only if bits 6-11 are 11000, i.e., S=1 and -256 <= D < -224). Instructions marked "restricted" can be executed only in ring zero.